集成電路版圖設計與Cadence工具入門講義

集成電路(IC)版圖設計是連接電路設計與芯片制造的關鍵環(huán)節(jié),它直接影響芯片的性能、面積和可靠性。本講義以Cadence平臺為例,系統(tǒng)性地介紹集成電路版圖設計的基礎知識、工具操作與研發(fā)實踐。

一、集成電路版圖設計概述

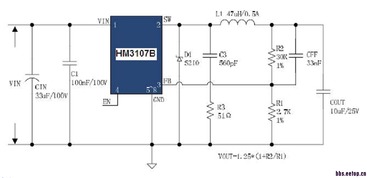

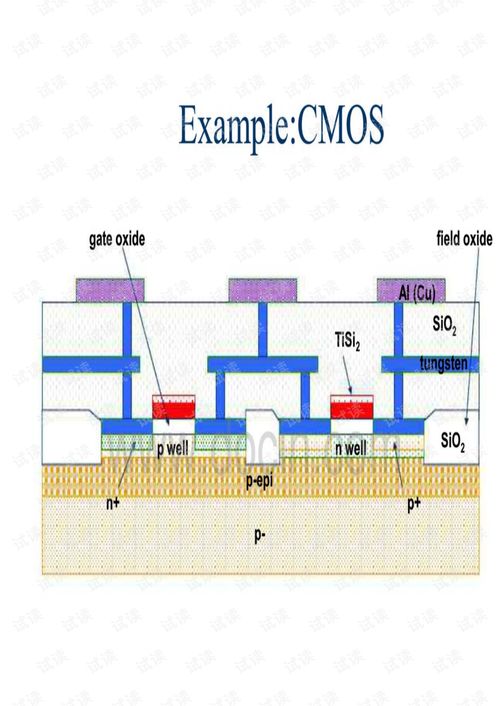

版圖設計是將電路網(wǎng)表轉化為一系列幾何圖形,這些圖形定義了芯片制造過程中各層的物理結構。版圖設計師需要深刻理解設計規(guī)則(Design Rules)、電氣規(guī)則(Electrical Rules)以及工藝制程的約束。一個優(yōu)秀的版圖需要在滿足所有規(guī)則的前提下,優(yōu)化面積、功耗、信號完整性和可制造性。

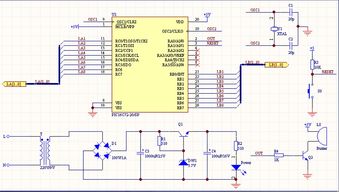

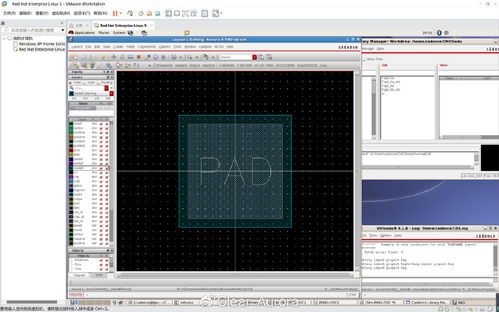

二、Cadence版圖設計環(huán)境

Cadence Virtuoso是業(yè)界廣泛采用的版圖編輯工具。其環(huán)境主要包括:

- 庫管理器(Library Manager):用于管理工藝庫、設計庫和單元。

- 版圖編輯器(Layout Editor):核心設計窗口,提供豐富的圖形繪制、編輯和驗證功能。

- 屬性編輯器(Property Editor):查看和修改設計對象的屬性。

三、版圖設計基礎操作

- 創(chuàng)建單元與實例化:從基本圖形(矩形、多邊形等)開始構建晶體管、接觸孔等基礎元件,并將其組合成更復雜的單元(Cell),通過實例化(Instance)實現(xiàn)層次化設計。

- 圖層與顯示控制:熟悉工藝設計套件(PDK)提供的各層定義(如金屬層、多晶硅層、擴散層等),并合理使用顯示過濾器(Display Resource)提高設計可視性。

- 約束驅動設計:利用約束管理器設置線寬、間距等規(guī)則,確保設計符合規(guī)范。

四、版圖驗證與后仿真

設計完成的版圖必須經(jīng)過嚴格的驗證:

- 設計規(guī)則檢查(DRC):確保版圖幾何圖形符合晶圓廠制定的制造規(guī)則。

- 電路圖與版圖一致性檢查(LVS):驗證版圖實現(xiàn)的電路與原始電路網(wǎng)表在電氣連接上完全一致。

- 寄生參數(shù)提取(PEX):提取版圖中的寄生電阻和電容,并進行后仿真(Post-layout Simulation),以評估版圖對電路性能(如速度、功耗)的實際影響。

五、研發(fā)實踐與進階技巧

在研發(fā)項目中,版圖設計需與電路設計團隊緊密協(xié)作:

- 匹配與對稱性:對于差分對、電流鏡等敏感電路,采用共質(zhì)心、交叉耦合等版圖技術以降低工藝偏差影響。

- 電源與地線規(guī)劃:設計穩(wěn)健的電源網(wǎng)絡(Power Grid),確保電流密度均勻,避免電遷移(Electromigration)問題。

- 信號完整性:對于高頻或敏感信號線,需考慮屏蔽、隔離和阻抗控制。

- 可制造性設計(DFM):采用添加冗余接觸孔、天線效應避免等技巧,提升芯片制造的良率。

六、與資源

掌握Cadence版圖設計工具是現(xiàn)代IC研發(fā)工程師的必備技能。建議讀者結合本講義,通過實際項目練習,并深入學習相關工藝文檔、參考設計和在線社區(qū)(如EETOP等專業(yè)論壇)的討論,不斷積累經(jīng)驗。版圖設計是藝術與工程的結合,唯有細心、耐心與創(chuàng)新,才能設計出高性能、高可靠的芯片。

如若轉載,請注明出處:http://m.b265.cn/product/38.html

更新時間:2026-04-26 06:18:23